### (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2018/0226287 A1

(43) **Pub. Date:**

# Aug. 9, 2018

### (54) MICRO-TRANSFER-PRINTABLE FLIP-CHIP STRUCTURES AND METHODS

(71) Applicant: X-Celeprint Limited, Cork (IE)

(72) Inventors: Christopher Bower, Raleigh, NC (US); Matthew Meitl, Durham, NC (US); António José Marques Trindade, Cork (IE); Ronald S. Cok, Rochester, NY (US); Brook Raymond, Cary, NC (US); Carl Prevatte, Raleigh, NC (US)

(21) Appl. No.: 15/944,223

(22) Filed: Apr. 3, 2018

### Related U.S. Application Data

- Continuation-in-part of application No. 15/811,959, filed on Nov. 14, 2017.

- (60) Provisional application No. 62/422,365, filed on Nov. 15, 2016.

### **Publication Classification**

(51) Int. Cl. H01L 21/683 (2006.01)H01L 21/67 (2006.01)H01L 25/075 (2006.01)

H01L 33/62 (2006.01)B65G 47/91 (2006.01)

U.S. Cl.

CPC .... H01L 21/6835 (2013.01); H01L 21/67144 (2013.01); H01L 25/0753 (2013.01); H01L *33/62* (2013.01); *H01L 2933/0066* (2013.01); H01L 2221/68318 (2013.01); H01L 2221/68363 (2013.01); H01L 2221/68381 (2013.01); **B65G** 47/91 (2013.01)

#### (57)ABSTRACT

In certain embodiments, a method of making a semiconductor structure suitable for transfer printing (e.g., micro-transfer printing) includes providing a support substrate and disposing and processing one or more semiconductor layers on the support substrate to make a completed semiconductor device. A patterned release layer and, optionally, a capping layer are disposed on or over the completed semiconductor device and the patterned release layer or capping layer, if present, are bonded to a handle substrate with a bonding layer. The support substrate is removed to expose the completed semiconductor device and, in some embodiments, a portion of the patterned release layer. In some embodiments, an entry path is formed to expose a portion of the patterned release layer. In some embodiments, the release layer is etched and the completed semiconductor devices transfer printed (e.g., micro-transfer printed) from the handle substrate to a destination substrate.

FIG. 11

FIG. 2B

FIG. 9

## MICRO-TRANSFER-PRINTABLE FLIP-CHIP STRUCTURES AND METHODS

### PRIORITY APPLICATIONS

[0001] This application is a continuation-in-part of U.S. patent application Ser. No. 15/811,959, filed Nov. 14, 2017, entitled "Micro-Transfer-Printable Flip-Chip Structures and Methods", which claims the benefit of U.S. Provisional Patent Application No. 62/422,365, filed Nov. 15, 2016, entitled "Micro-Transfer-Printable Flip-Chip Structure and Method", the disclosure of each of which is hereby incorporated by reference in its entirety.

## CROSS REFERENCE TO RELATED APPLICATIONS

[0002] Reference is made to U.S. Pat. No. 9,368,683, issued Jun. 14, 2016, entitled "Printable Inorganic Semiconductor Method", the contents of which are incorporated by reference herein in their entirety.

### FIELD OF THE INVENTION

[0003] The present invention relates to structures and methods for providing micro-integrated circuits on flip-chip substrates that can be printed using massively parallel micro-transfer printing methods.

### BACKGROUND OF THE INVENTION

[0004] Integrated circuits (ICs) are widely used in electronic devices. Integrated circuits are typically formed on a semiconductor wafer using photolithographic processes and then packaged, for example in a ceramic or plastic package, with pins or bumps on the package providing externally accessible electrical connections to the integrated circuit. An unpackaged integrated circuit is often referred to as a die. Each die typically has electrical contact pads on the top of the integrated circuit that are electrically connected to electronic circuits in the integrated circuit. The die is placed in a cavity in the package, the electrical contact pads are wire-bonded to the package pins or bumps, and the package is sealed. Frequently, multiple identical devices are formed in the semiconductor wafer and the wafer is cut (for example by scribing-and-breaking or by sawing the wafer) into separate integrated circuit dies that are each individually packaged. The packages are then mounted and electrically connected on a printed circuit board to make an electronic

[0005] In an alternative flip-chip approach, small spheres of solder (solder bumps) are deposited on the integrated circuit contact pads and the integrated circuit is flipped over so that the top side of the die with the solder bumps is located adjacent to the package or other destination substrate. This approach is particularly useful for packages such as pin-grid array packages because they can require less space than a wire-bond process. However, flipping the integrated circuit over can be difficult for very small integrated circuits, for example having a dimension of less than 200, less than 50 microns, less than 20 microns, less than 10 microns, or less than 5 microns. Such small integrated circuit dies are not easily handled without loss or damage using conventional pick-and-place or vacuum tools.

[0006] In some applications, the bare integrated circuit dies are not separately packaged but are placed on a destination substrate and electrically connected on the destination

substrate, for example using photolithographic or printed-circuit board methods, to form an electronic system. However, as with flip-chip handling, this can be difficult to accomplish when the integrated circuit dies are small. However, an efficient method of transferring bare dies from a relatively small and expensive source substrate (e.g., crystalline semiconductor) to a relatively large and inexpensive destination substrate (e.g., amorphous glass or plastic) is very desirable, since the integrated circuits can provide much higher data processing efficiency than thin-film semiconductor structures formed on large substrates.

[0007] In another method, a handle substrate is adhered to the side of the integrated circuits opposite the wafer (the top side), the wafer is removed, for example by grinding, the integrated circuits are adhered to the destination substrate, and the handle substrate is removed. In yet another variation, the handle substrate is the destination substrate and is not removed. In this case, the integrated circuit is flipped over so that the top side of the integrated circuit is adhered to the destination substrate.

[0008] In yet another method, epitaxial semiconductor layers are formed on a growth substrate, for example a sapphire substrate. A handle substrate is adhered to the top side of the semiconductor layers opposite the growth substrate, and the growth substrate is removed. The flipped semiconductor layers are then processed to form the integrated circuits. For example, U.S. Pat. No. 6,825,559 describes such a method to make light emitting diodes.

[0009] One approach to handling and placing small integrated circuits (e.g., chiplets) uses micro-transfer printing, for example as described in U.S. Pat. Nos. 8,722,458, 7,622,367 and 8,506,867, each of which is hereby incorporated by reference in its entirety. In exemplary embodiments of these methods for printing integrated circuits, an integrated circuit is disposed (e.g., formed) on a source wafer, for example a semiconductor wafer, and undercut by etching a gap between a bottom side of the integrated circuit and the wafer. A stamp contacts a top side of the integrated circuit to adhere the integrated circuit to the stamp, the stamp and integrated circuit are transported to a destination substrate, for example a glass or plastic substrate, the integrated circuit is contacted and adhered to the destination substrate, and the stamp removed to "print" the integrated circuit from the source wafer to the destination substrate. Multiple integrated circuits can be "printed" in a common step with a single stamp. The integrated circuits can then be electrically connected, for example, using conventional photolithographic and printed-circuit board methods. These techniques have the advantage of enabling location of many (e.g., tens of thousands to millions) small integrated circuit devices on a destination substrate in a single print step. For example, U.S. Pat. No. 8,722,458 teaches, inter alia, transferring lightemitting, light-sensing, or light-collecting semiconductor elements from a wafer substrate to a destination substrate using a patterned elastomer stamp whose spatial pattern matches the location of the semiconductor elements on the wafer substrate.

[0010] None of the aforementioned flip-chip methods form a flipped integrated circuit that can be micro-transfer printed. Moreover, GaN micro-LEDs are typically formed on sapphire substrates since sapphire has a smaller crystal lattice mismatch with GaN than other materials, such as silicon. Thus, it is desirable to form printable integrated circuit structures, such as micro-LEDs, using a sapphire

substrate. However, there is no available method for undercutting a chiplet formed on a sapphire substrate to enable release of the chiplet for micro-transfer printing.

[0011] There is a need, therefore, for wafer and integrated circuit structures and methods that provide flipped microtransfer printable integrated circuits and for structures and methods that enable the construction of micro-LED chiplets formed on a sapphire substrate that can be micro-transfer printed. There is also a need for simple and inexpensive methods and structures having a reduced area that enable electrical interconnections for chiplets printed on destination substrates. Furthermore, there is a need for methods and structures that enable electrically connecting the electrical contacts of printed structures, such as printed LEDs, using fewer processing steps than conventional methods.

### SUMMARY OF THE INVENTION

[0012] In certain embodiments, a method of making a semiconductor structure suitable for micro-transfer printing comprises: providing a support substrate; disposing one or more semiconductor layers in, on, or over the support substrate, and optionally processing the semiconductor layers, to make a completed semiconductor device; forming a patterned release layer on or over the completed semiconductor device and optionally at least partly in contact with the support substrate; optionally providing a capping layer on the patterned release layer; providing a handle substrate; disposing a conformable and curable bonding layer on the patterned release layer, on the optional capping layer, or on the handle substrate; locating the handle substrate in contact with the bonding layer and curing the bonding layer to bond the handle substrate to the patterned release layer or to the capping layer; removing the support substrate to expose the completed semiconductor device and optionally expose a portion of the patterned release layer; and if at least a portion of the patterned release layer is not exposed, forming an entry path to expose a portion of the patterned release layer. In certain embodiments, a method comprises removing at least a portion of a patterned release layer to form a gap or space between at least a portion of a completed semiconductor device and at least a portion of a bonding layer and to form a tether physically connecting the completed semiconductor device to an anchor disposed on the handle substrate (e.g., wherein the anchor is a portion of the handle substrate or a layer disposed on the handle substrate, such as, for example, a bonding layer, a capping layer, or a dielectric layer). A tether can be disposed in a common plane with an entry path and can be fractured when a completed semiconductor device is micro-transfer printed or the tether can be disposed between the completed semiconductor device and the handle substrate, for example as a post with a physical interface to the completed semiconductor device.

[0013] A semiconductor structure can include a plurality of completed semiconductor devices and each of the plurality of completed semiconductor devices can have an individual tether and an individual anchor physically connecting the completed semiconductor devices to other structures or layers in the semiconductor structure, such as a bonding or capping layer(s). In some embodiments, at least two of a plurality of completed semiconductor devices have a common structure providing tethers for each completed semiconductor device or a common anchor structure to which the tethers are physically connected. At least two of a plurality of completed semiconductor devices can have a

common anchor structure that is a ridge of material that contacts two or more completed semiconductor devices.

[0014] A removal layer such as an ablation or etch-stop layer can be provided between semiconductor layer(s) and a support substrate. In some embodiments, a destination substrate is provided and a completed semiconductor device is micro-transfer printed from a handle substrate to the destination substrate.

[0015] In some embodiments, a support substrate is removed by one or more of laser liftoff, ablation, laser ablation, etching, and grinding. A support substrate can be transparent to electromagnetic radiation and removing the support substrate can expose a semiconductor layer to electromagnetic radiation through the support substrate to decompose a portion of the semiconductor layer(s) or completed semiconductor device and form a shock wave in the semiconductor structure. Alternatively, an ablation layer is provided between a support substrate and semiconductor layer(s) and the support substrate is removed by exposing the ablation layer to electromagnetic radiation through the support substrate to decompose a portion of the ablation layer and form a shock wave in a completed semiconductor structure. A capping layer can have a thickness, layers, structure, and material sufficient to disperse, deflect, reflect, or absorb a shock wave produced by laser ablation of at least a portion of a ablation layer, a portion of a semiconductor layer, or a portion of a completed semiconductor device.

[0016] In some embodiments, a support substrate is a semiconductor substrate and disposing one or more semiconductor layers in, on, or over the support substrate includes doping (e.g., implanting) a portion or layer of the semiconductor substrate. Alternatively, or in addition, disposing one or more semiconductor layers in, on, or over a support substrate can include growing the one or more semiconductor layers on the support substrate or growing the one or more semiconductor layers on a growth layer or semiconductor seed layer on the support substrate.

[0017] A semiconductor structure suitable for micro-transfer printing can include: a handle substrate; a conformable, cured bonding layer disposed in contact with the handle substrate; an optional capping layer disposed in contact with the bonding layer; a patterned release layer disposed in contact with the cured bonding layer or the capping layer, wherein the patterned release layer has an entry path; and a completed semiconductor device disposed on or over the patterned release layer and attached to an anchor disposed on the handle substrate with at least one tether.

[0018] A support substrate can be one or more of sapphire, quartz, silicon, GaAs, GaN, InP, SiC, GaP, GaSb, AN, and MgO. A completed semiconductor device can include one or more of a semiconductor material, a compound semiconductor material, GaN, Si, InP, SiGe, and GaAs. A patterned release layer includes one or more of germanium, Si, TiW, Al, Ti, a lift-off resist, and a polymer. A support substrate can be a growth substrate, have a semiconductor seed layer, or have a semiconductor layer. A cured bonding layer can be a cured resin, SU-8, epoxy, a metal layer, a metal alloy layer, a solder layer, or a layer of AuSn.

[0019] In some embodiments, a completed semiconductor device is exposed and/or an entry path is exposed. In some embodiments, a removal layer is only a portion of the completed semiconductor device. In some embodiments, a removal layer is in contact with a completed semiconductor device and is disposed on or over, or is a part of, a support

substrate. A support substrate can be in contact with a removal layer or with a completed semiconductor device. A capping layer can include a plurality of layers.

[0020] In some embodiments, a completed semiconductor device includes a semiconductor structure with at least two electrical contacts to the completed semiconductor device that are in different planes. A completed semiconductor device can include an electrically separate electrode electrically connected to each of the electrical contacts and exposed portions of the electrodes are in a common plane. Exposed portions of the electrodes are used to make electrical contact to external electrical conductors.

[0021] A destination substrate onto which the completed semiconductor device is micro-transfer printed can have a non-planar surface with a topography that corresponds to a non-planar semiconductor structure surface to facilitate electrical connections between the completed semiconductor device and electrical contact pads on the destination substrate.

[0022] In some embodiments, an electrical contact is disposed on the side of a completed semiconductor device adjacent to a support substrate or on the side of the completed semiconductor device adjacent to a patterned release layer. Each electrical contact can include or be connected to a connection post. In some embodiments, an electrode is electrically connected to each electrical contact and a connection post is electrically connected to each electrode or the electrode includes or forms a connection post. A connection post can have a first surface adjacent to a surface of the completed semiconductor device and a second opposing surface farther away from the completed semiconductor device than the first surface. The second opposing surface can have a smaller area than the first surface. Furthermore, a connection post can have a height that is greater than a dimension of the first surface, the connection post can have a height that is greater than a dimension of the second opposing surface, or the connection post can have a height that is greater than a width of the connection post.

[0023] In one aspect, the present invention is directed to a method of making a semiconductor structure suitable for transfer printing (e.g., micro-transfer printing), comprising: providing a support substrate; forming a completed semiconductor device disposed in, on, or over the support substrate; forming a patterned release layer on or over the completed semiconductor device; providing a capping layer on the patterned release layer; providing a handle substrate; disposing a conformable and curable bonding layer on the capping layer or on the handle substrate; disposing the handle substrate and the capping layer in contact with the bonding layer; curing the bonding layer to bond the handle substrate to the capping layer; and removing the support substrate to expose the completed semiconductor device (e.g., thereby exposing the completed semiconductor device).

[0024] In certain embodiments, the method comprises forming an entry path to expose a portion of the patterned release layer. In certain embodiments, the method comprises removing at least a portion of the patterned release layer to form a gap between at least a portion of the completed semiconductor device and at least a portion of the bonding layer; and forming a tether physically connecting the completed semiconductor device to an anchor disposed on the handle substrate (e.g., wherein the anchor is a portion of the handle substrate or a layer disposed on the handle substrate,

such as, for example, the bonding layer, the capping layer, or a dielectric layer). In certain embodiments, the method comprises: providing a destination substrate; and microtransfer printing the completed semiconductor device from the handle substrate to the destination substrate.

[0025] In certain embodiments, the support substrate is transparent to electromagnetic radiation and the method comprises: exposing the semiconductor layer to electromagnetic radiation through the support substrate to decompose a portion of the completed semiconductor device and form a shock wave in the semiconductor structure, wherein the capping layer disperses, reflects, deflects, or absorbs the shock wave. In certain embodiments, the support substrate is transparent to electromagnetic energy, and the method comprises: providing an ablation layer between the support substrate and the completed semiconductor device; and exposing the ablation layer to electromagnetic radiation through the support substrate to decompose a portion of the ablation layer and form a shock wave in the completed semiconductor structure, wherein the capping layer disperses, reflects, deflects, or absorbs the shock wave.

[0026] In certain embodiments, removing the support substrate comprises one or more of laser liftoff, ablation, laser ablation, etching, and grinding. In certain embodiments, the method comprises providing an ablation or etch-stop layer between the completed semiconductor device and the support substrate. In certain embodiments, removing the support substrate to expose the completed semiconductor device comprises removing a removal layer (e.g., an ablation layer or an etch-stop layer) (e.g., thereby exposing the completed semiconductor layer).

[0027] In certain embodiments, the support substrate is a semiconductor substrate and forming the completed semiconductor device comprises: doping a portion or layer of the semiconductor substrate. In certain embodiments, forming the completed semiconductor device comprises: disposing one or more semiconductor layers in, on, or over the support substrate. In certain embodiments, forming the completed semiconductor device comprises growing the one or more semiconductor layers on the support substrate or on a growth layer on the support substrate. In certain embodiments, forming the completed semiconductor device comprises: processing the one or more semiconductor layers.

[0028] In another aspect, the present invention is directed to a method of making a semiconductor structure suitable for transfer printing (e.g., micro-transfer printing), comprising: providing a support substrate; forming a completed semiconductor device disposed in, on, or over the support substrate; forming a patterned release layer on or over the completed semiconductor device; providing a handle substrate; disposing a conformable and curable bonding layer on the patterned release layer or on the handle substrate; disposing the handle substrate and the patterned release layer in contact with the bonding layer; curing the bonding layer to bond the handle substrate to the patterned release layer; and removing the support substrate to expose the completed semiconductor device (e.g., thereby exposing the completed semiconductor device).

[0029] In certain embodiments, the method comprises disposing the conformable and curable bonding layer on the patterned release layer, wherein disposing the conformable and curable bonding layer on the patterned release layer comprises disposing the conformable and curable bonding layer on at least one of (i) a portion of a dielectric layer

disposed on the completed semiconductor structure and (ii) a portion of the completed semiconductor structure.

[0030] In certain embodiments, the method comprises removing at least a portion of the patterned release layer to form a gap between at least a portion of the completed semiconductor device and at least a portion of the bonding layer; and forming a tether physically connecting the completed semiconductor device to an anchor disposed on the handle substrate (e.g., wherein the anchor is a portion of the handle substrate or a layer disposed on the handle substrate, such as, for example, the bonding layer or a dielectric layer). In certain embodiments, the method comprises providing a destination substrate; and micro-transfer printing the completed semiconductor device from the handle substrate to the destination substrate.

[0031] In certain embodiments, removing the support substrate comprises one or more of laser liftoff, ablation, laser ablation, etching, and grinding. In certain embodiments, the method comprises providing an ablation or etch-stop layer between the completed semiconductor device and the support substrate. In certain embodiments, removing the support substrate to expose the completed semiconductor device comprises removing a removal layer (e.g., an ablation layer or an etch-stop layer) (e.g., thereby exposing the completed semiconductor device).

[0032] In certain embodiments, the support substrate is a semiconductor substrate and forming the completed semiconductor device comprises: doping a portion or layer of the semiconductor substrate. In certain embodiments, forming the completed semiconductor device comprises: disposing one or more semiconductor layers in, on, or over the support substrate. In certain embodiments, forming the completed semiconductor device comprises: growing the one or more semiconductor layers on the support substrate or on a growth layer on the support substrate. In certain embodiments, forming the completed semiconductor device comprises: processing the one or more semiconductor layers.

[0033] In another aspect, the present invention is directed to a semiconductor structure suitable for transfer printing (e.g., micro-transfer printing), comprising: a handle substrate; a cured bonding layer disposed in contact with the handle substrate; a patterned release layer disposed in contact with the cured bonding layer; and a completed semiconductor device disposed on or over the patterned release layer and attached to an anchor disposed on the handle (e.g., wherein the anchor is a portion of the handle substrate or a layer disposed on the handle substrate, such as, for example, the bonding layer or a dielectric layer) substrate with at least one tether.

[0034] In certain embodiments, at least one of the completed semiconductor device and a portion of the patterned release layer is exposed.

[0035] In certain embodiments, a portion of the completed semiconductor device is a removal layer or the semiconductor structure comprises a removal layer in contact with the completed semiconductor device.

[0036] In certain embodiments, the semiconductor structure comprises a support substrate in contact with the removal layer. In certain embodiments, the semiconductor structure comprises a support substrate in contact with the completed semiconductor device.

[0037] In certain embodiments, the completed semiconductor device comprises a semiconductor structure comprising at least two electrical contacts to the completed semi-

conductor device that are in different planes. In certain embodiments, the completed semiconductor device comprises an electrically separate electrode electrically connected to each of the electrical contacts, wherein exposed portions of the electrodes are in a common plane. In certain embodiments, the semiconductor structure comprises a destination substrate having a non-planar surface that corresponds to a non-planar surface of the completed semiconductor structure.

[0038] In certain embodiments, the support substrate comprises one or more of sapphire, quartz, silicon, GaAs, GaN, InP, SiC, GaP, GaSb, AlN, and MgO. In certain embodiments, the completed semiconductor device comprises one or more of a semiconductor material, a compound semiconductor material, GaN, Si, InP, SiGe, and GaAs. In certain embodiments, the patterned release layer comprises one or more of germanium, Si, TiW, Al, Ti, a lift-off resist, and a polymer.

[0039] In certain embodiments, the semiconductor structure comprises one or more electrical contacts on a side of the completed semiconductor device adjacent to the patterned release layer or one or more electrical contacts on a side of the completed semiconductor device opposite the side of the completed semiconductor device adjacent to the patterned release layer (e.g., a side adjacent to a support substrate in the semiconductor structure).

[0040] In certain embodiments, (i) each electrical contact comprises a connection post or (ii) the semiconductor structure comprises an electrode electrically connected to each electrical contact and a connection post electrically connected to each electrode (e.g., wherein the electrode comprises or forms a connection post). In certain embodiments, each connection post is tapered (e.g., has a first surface adjacent to a surface of the completed semiconductor device and a second opposing surface and the second opposing surface has a smaller area than an area of the first surface). In certain embodiments, each connection post has a height to width aspect ratio of greater than 1:1.

[0041] In certain embodiments, the at least one tether is disposed between the completed semiconductor device and the handle substrate.

[0042] In certain embodiments, the semiconductor structure comprises a plurality of completed semiconductor devices, wherein each of the plurality of completed semiconductor devices comprises an individual tether connected to a unique anchor. In certain embodiments, the semiconductor structure comprises a plurality of completed semiconductor devices, wherein at least two of the plurality of completed semiconductor devices are physically connected by respective tethers to a common anchor structure. In certain embodiments, at least two of the plurality of completed semiconductor devices are connected to a common anchor structure that is a ridge of bonding layer material.

[0043] In certain embodiments, the support substrate is a growth substrate. In certain embodiments, the support substrate comprises a semiconductor layer or a semiconductor seed layer. In certain embodiments, the cured bonding layer comprises at least one of a cured resin, an epoxy, a metal layer, a metal alloy layer, a solder layer, and a layer of AuSn.

[0044] In certain embodiments, surfaces at opposing edges of the completed semiconductor device are in a common plane, wherein a first electrical contact is located at the bottom of a well, pit, or depression in the completed semiconductor device and is electrically connected to a first

electrode, wherein a second electrical contact electrically separate from the first electrical contact is electrically connected to a second electrode, and wherein the first electrode has a greater height than the height of the second electrode so that exposed portions of the first and second electrodes are in a common plane.

[0045] In another aspect, the present invention is directed to a semiconductor structure suitable for transfer printing (e.g., micro-transfer printing), comprising: a handle substrate; a cured bonding layer disposed in contact with the handle substrate; a capping layer disposed in contact with the bonding layer; a patterned release layer disposed in contact with the capping layer; and a completed semiconductor device disposed on or over the patterned release layer and attached to an anchor disposed on the handle substrate with at least one tether (e.g., wherein the anchor is a portion of the handle substrate or a layer disposed on the handle substrate, such as, for example, the bonding layer, the capping layer, or a dielectric layer).

[0046] In certain embodiments, at least one of the completed semiconductor device and a portion of the patterned release layer is exposed. In certain embodiments, a portion of the completed semiconductor device is a removal layer or the semiconductor structure comprises a removal layer in contact with the completed semiconductor device. In certain embodiments, the semiconductor structure comprises a support substrate in contact with the removal layer. In certain embodiments, a support substrate in contact with the completed semiconductor device.

[0047] In certain embodiments, the capping layer has a thickness sufficient to disperse, deflect, reflect, or absorb a shock wave produced by laser ablation of at least a portion of the removal layer. In certain embodiments, the capping layer has a thickness sufficient to disperse, deflect, reflect or absorb a shock wave produced by laser ablation of a portion of the completed semiconductor device. In certain embodiments, the capping layer comprises a plurality of layers.

[0048] In certain embodiments, the completed semiconductor device comprises a semiconductor structure comprising at least two electrical contacts to the completed semiconductor device that are in different planes. In certain embodiments, the completed semiconductor device comprises an electrically separate electrode electrically connected to each of the electrical contacts, wherein exposed portions of the electrodes are in a common plane.

[0049] In certain embodiments, the semiconductor structure comprises a destination substrate having a non-planar surface that corresponds to a non-planar surface of the completed semiconductor structure.

[0050] In certain embodiments, the support substrate comprises one or more of sapphire, quartz, silicon, GaAs, GaN, InP, SiC, GaP, GaSb, AlN, and MgO. In certain embodiments, the completed semiconductor device comprises one or more of a semiconductor material, a compound semiconductor material, GaN, Si, InP, SiGe, and GaAs. In certain embodiments, the patterned release layer comprises one or more of germanium, Si, TiW, Al, Ti, a lift-off resist, or a polymer.

[0051] In certain embodiments, the semiconductor structure comprises one or more electrical contacts on a side of the completed semiconductor device adjacent to the patterned release layer or one or more electrical contacts on a side of the completed semiconductor device opposite the side of the completed semiconductor device adjacent to the

patterned release layer (e.g., a side adjacent to a support substrate in the semiconductor structure).

[0052] In certain embodiments, each electrical contact comprises a connection post or (ii) the semiconductor structure comprises an electrode electrically connected to each electrical contact and a connection post electrically connected to each electrode (e.g., wherein the electrode comprises or forms a connection post). In certain embodiments, each connection post is tapered (e.g., has a first surface adjacent to a surface of the completed semiconductor device and a second opposing surface and the second opposing surface has a smaller area than an area of the first surface). In certain embodiments, each connection post has a height to width aspect ratio of greater than 1:1.

[0053] In certain embodiments, a surface of the at least one tether is disposed in a common plane a surface of the completed semiconductor device. In certain embodiments, the semiconductor structure comprises a plurality of completed semiconductor devices, wherein each of the plurality of completed semiconductor devices comprises an individual tether connected to a unique anchor. In certain embodiments, the semiconductor structure comprises a plurality of completed semiconductor devices, wherein at least two of the plurality of completed semiconductor devices are physically connected by respective tethers to a common anchor structure.

[0054] In some embodiments of the present invention, a method of making a semiconductor structure suitable for transfer printing comprises providing a support substrate, providing a semiconductor support layer over the support substrate, providing a semiconductor layer disposed over the semiconductor support layer, forming a plurality of semiconductor devices disposed in, on, or over the semiconductor support layer, each of the semiconductor devices comprising one or more electrical contacts exposed on a side of the semiconductor device opposite the semiconductor support layer, forming a connection post on each of the exposed electrical contacts, the connection posts extending in a direction away from the semiconductor support layer, patterning the semiconductor layer to separate the semiconductor devices in order to form a corresponding plurality of completed semiconductor devices, patterning the semiconductor support layer to expose a portion of the support substrate, forming a patterned release layer on or over the plurality of completed semiconductor devices, the patterned release layer (i) in contact with portions of the patterned semiconductor support layer on which the complete semiconductor devices are disposed and (ii) in contact with at least a portion of the support substrate, providing a handle substrate, disposing a conformable bonding layer on the patterned release layer or on the handle substrate, bonding the handle substrate to the patterned release layer with the bonding layer, and removing the support substrate to expose at least a portion of the patterned semiconductor support layer.

[0055] In some embodiments, methods of the present invention comprise disposing a capping layer over the patterned release layer, wherein the capping layer disperses, deflects, reflects, or absorbs a shock wave produced by laser ablation of at least a portion of the support substrate or semiconductor support layer.

[0056] In some embodiments, methods of the present invention comprise removing at least a portion of the patterned release layer to form a gap between at least a

portion of the completed semiconductor device and at least a portion of the bonding layer, and forming tethers physically connecting the plurality of completed semiconductor devices to anchors disposed on the handle substrate.

[0057] In some embodiments of the present invention, the anchors are disposed laterally between ones of the plurality of completed semiconductor devices and each of the tethers extends laterally from one of the completed micro-device to one of the anchors. Each of the tethers can be a portion of the semiconductor support layer.

[0058] Methods of the present invention can comprise micro-transfer printing the completed semiconductor devices from the handle substrate to a destination substrate and electrically contacting the connection posts to corresponding electrical contact pads on the destination substrate. Removing the support substrate can comprise one or more of laser liftoff, ablation, laser ablation, etching, and grinding. [0059] In some embodiments of the present invention, the semiconductor support layer is an ablation layer, a removal layer, or an etch-stop layer disposed between the completed

semiconductor support layer is an ablation layer, a removal layer, or an etch-stop layer disposed between the completed semiconductor device and the support substrate. Removing the support substrate can comprise removing a removal layer.

[0060] In certain embodiments of the present invention, a semiconductor structure suitable for transfer printing comprises a handle substrate, a bonding layer disposed in contact with the handle substrate, a patterned release layer disposed in contact with the bonding layer, a plurality of completed semiconductor devices disposed on or over the patterned release layer and each attached to one or more anchors disposed on the handle substrate with at least one tether, each of the plurality of completed semiconductor devices comprising at least one electrical contact disposed on a side of the completed semiconductor device between the completed semiconductor device and the handle substrate, a connection post disposed on each of the at least one electrical contacts and extending from the electrical contact toward the handle substrate, and a patterned semiconductor support layer comprising a surface on which is disposed the plurality of completed semiconductor devices and wherein the surface is in contact with a portion of the patterned release layer.

[0061] In some embodiments, a portion of the patterned release layer is exposed. In some embodiments, a portion of the plurality of completed semiconductor devices or the semiconductor support layer is or comprises a removal layer. [0062] In some embodiments of the present invention, a semiconductor structure comprises a support substrate in contact with the patterned semiconductor support layer and in contact with a portion of the patterned release layer. The support substrate can comprise a removal layer.

[0063] In certain embodiments, the patterned release layer defines a gap between the plurality of completed semiconductor devices and the bonding layer. In some embodiments of the present invention, a semiconductor structure suitable for transfer printing comprises a handle substrate, a bonding layer disposed in contact with the handle substrate, a capping layer disposed in contact with the bonding layer, a patterned release layer disposed in contact with capping layer, a plurality of completed semiconductor devices disposed on or over the patterned release layer and each attached to at least one anchor disposed on the handle substrate with at least one tether, each of the plurality of completed semiconductor devices comprising at least one

electrical contact disposed on a side of the completed semiconductor device between the completed semiconductor device and the handle substrate, a connection post disposed on each of the at least one electrical contacts and extending from the electrical contact toward the handle substrate, and a patterned semiconductor support layer comprising a surface on which is disposed the completed semiconductor devices and wherein the surface is in contact with a portion of the patterned release layer.

[0064] In some embodiments of the present invention, a portion of the patterned release layer is exposed. In some embodiments of the present invention, the semiconductor structure comprises a support substrate in contact with the semiconductor support layer and in contact with a portion of the patterned release layer.

[0065] In some embodiments of the present invention, a portion of the plurality of completed semiconductor devices or the semiconductor support layer is a removal layer, or the semiconductor structure comprises a removal layer in contact with the completed semiconductor device. The support substrate can comprise a removal layer.

[0066] In certain embodiments, the support substrate is a growth substrate. In certain embodiments, the support substrate comprises a semiconductor layer or a semiconductor seed layer. In certain embodiments, the cured bonding layer comprises at least one of a cured resin, an epoxy, a metal layer, a metal alloy layer, a solder layer, and a layer of AuSn.

[0067] In certain embodiments, surfaces at opposing edges of the completed semiconductor device are in a common plane, wherein a first electrical contact is located at the bottom of a well, pit, or depression in the completed semiconductor device and is electrically connected to a first electrode, wherein a second electrical contact electrically separate from the first electrical contact is electrically connected to a second electrode, and wherein the first electrode has a greater height than the height of the second electrodes or that exposed portions of the first and second electrodes are in a common plane.

### BRIEF DESCRIPTION OF THE DRAWINGS

**[0068]** The foregoing and other objects, aspects, features, and advantages of the present disclosure will become more apparent and better understood by referring to the following description taken in conjunction with the accompanying drawings, in which:

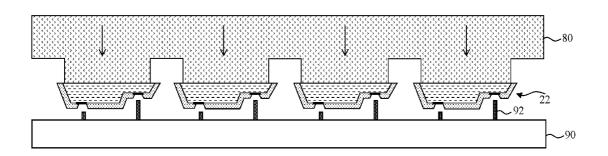

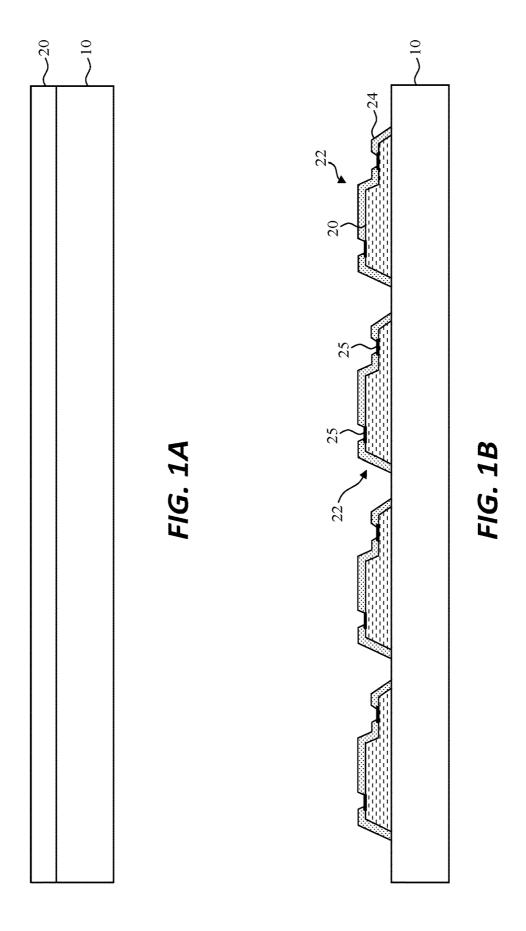

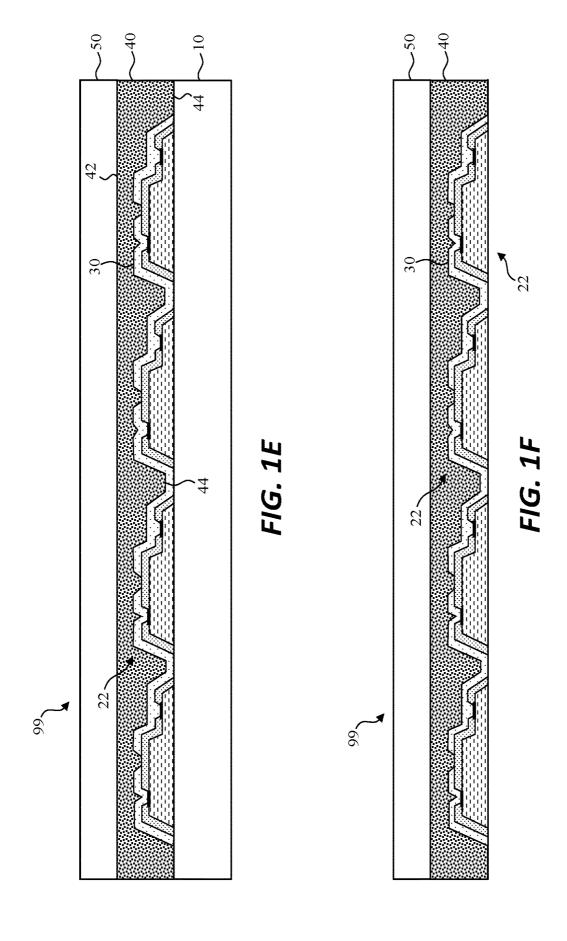

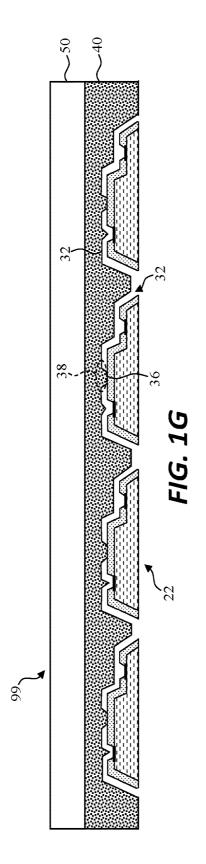

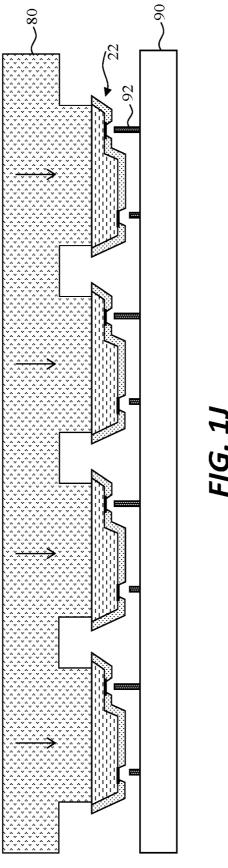

[0069] FIGS. 1A-1J are successive cross sections illustrating (i) sequential steps in an exemplary method and (ii) a semiconductor structure, according to illustrative embodiments of the present invention;

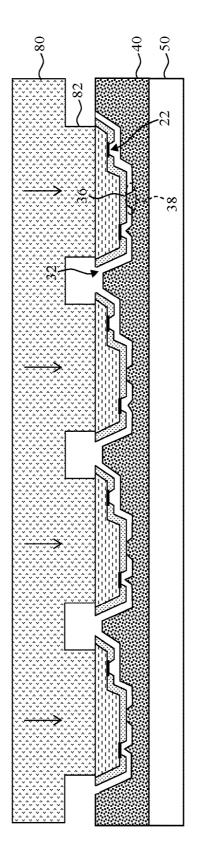

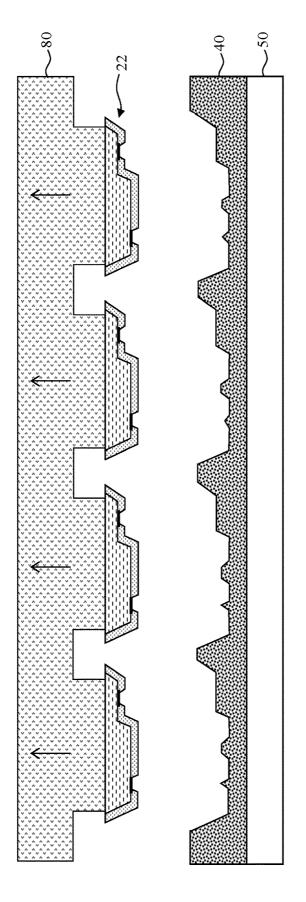

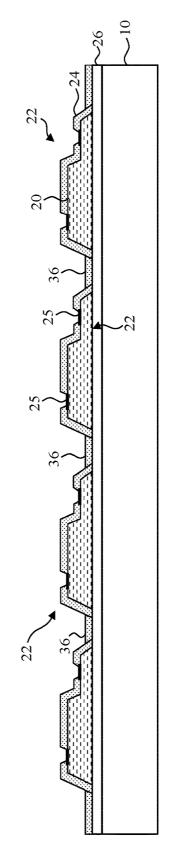

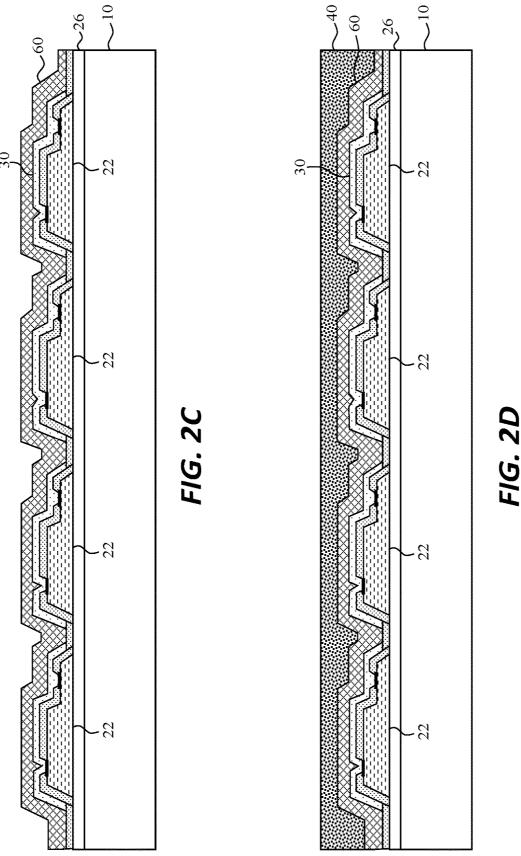

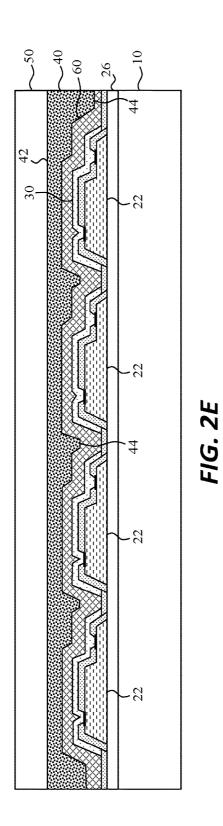

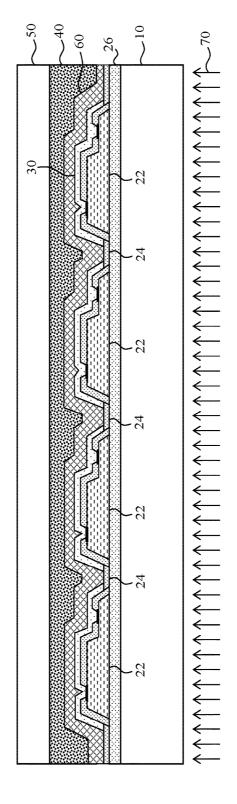

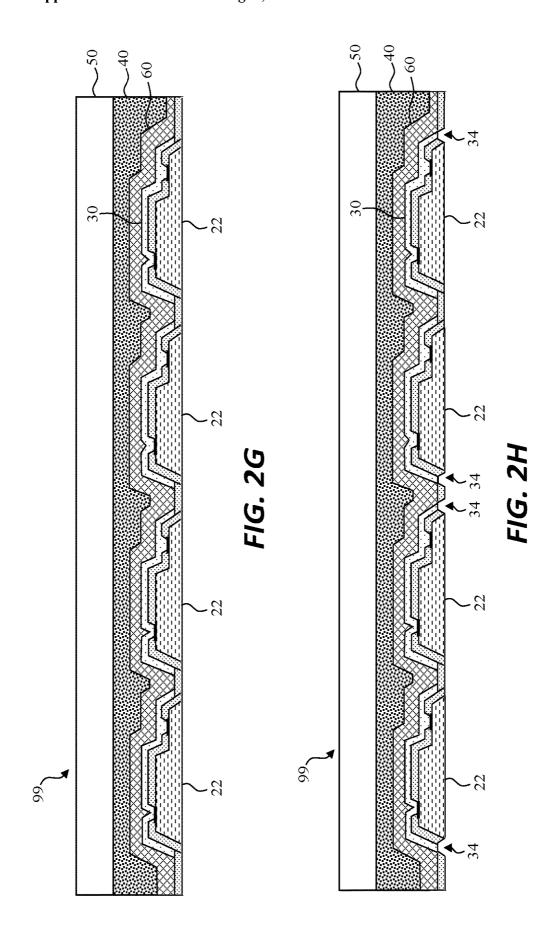

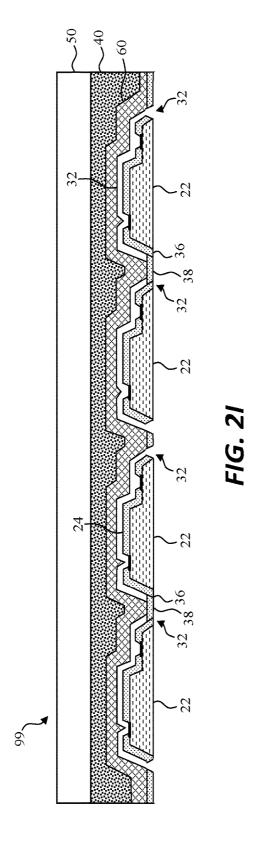

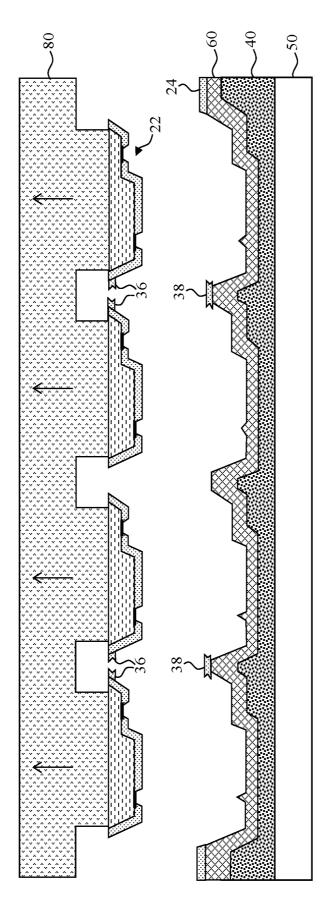

[0070] FIGS. 2A-2K are successive cross sections illustrating sequential steps in another exemplary method and (ii) another semiconductor structure, according to illustrative embodiments of the present invention;

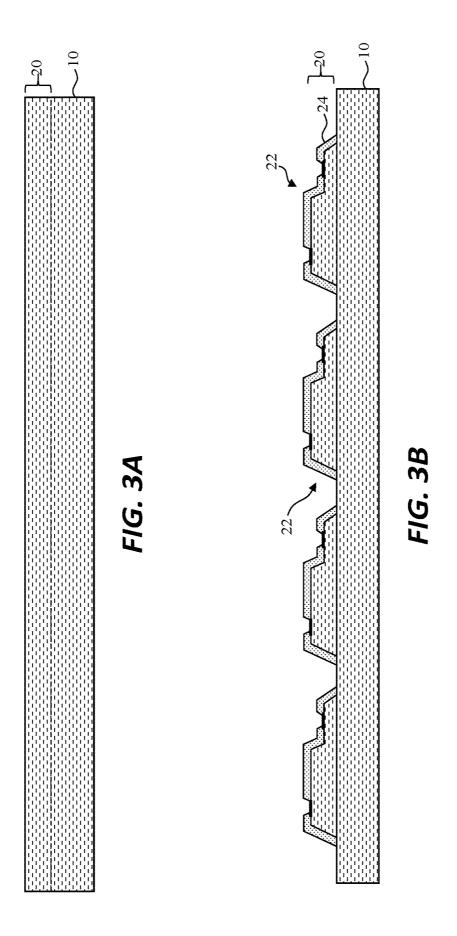

[0071] FIGS. 3A-3B are successive cross sections illustrating sequential steps in an exemplary method, according to illustrative embodiments of the present invention;

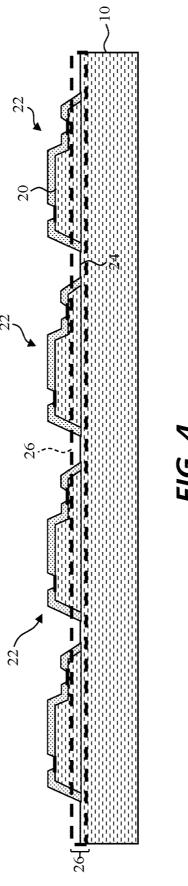

[0072] FIG. 4 is a cross section illustrating a semiconductor device with an ablation layer, according to illustrative embodiments of the present invention;

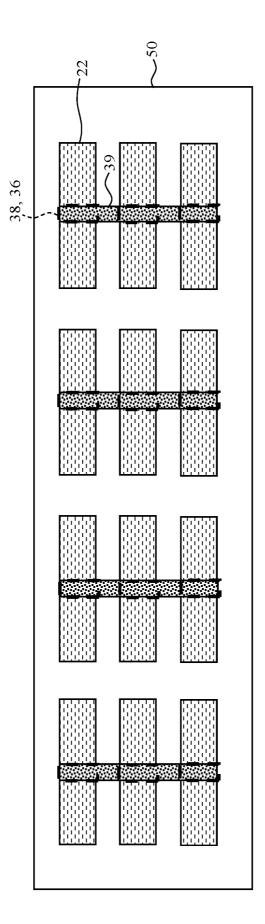

[0073] FIG. 5 is a plan view illustrating anchor, an anchor structure, and semiconductor devices on a source substrate, according to illustrative embodiments of the present invention:

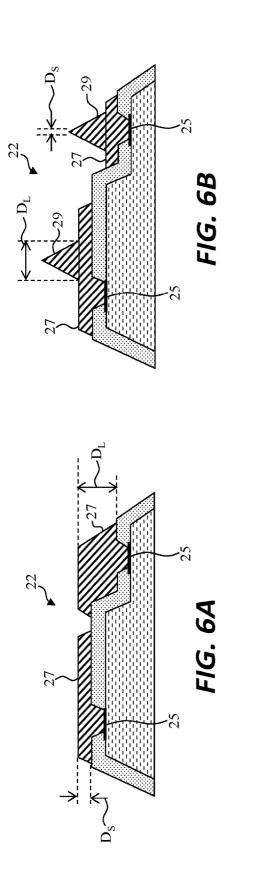

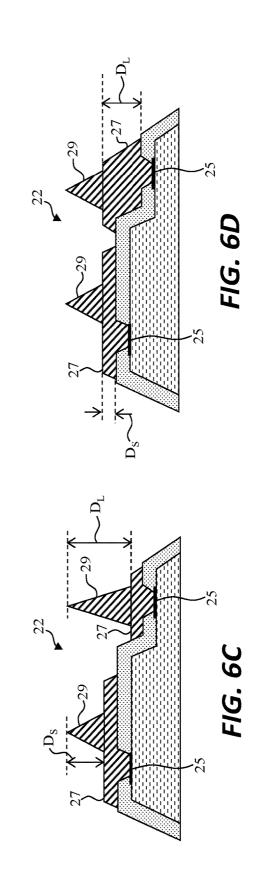

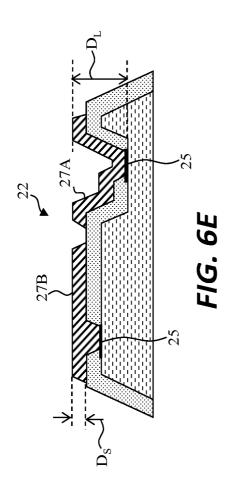

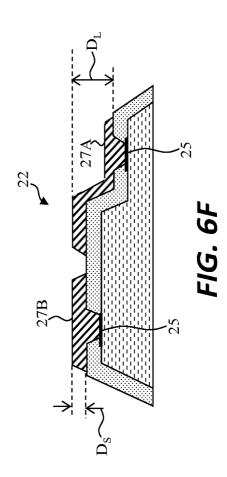

[0074] FIGS. 6A-6F are cross sections illustrating a variety of completed semiconductor devices with a corresponding variety of connection post structures, according to illustrative embodiments of the present invention;

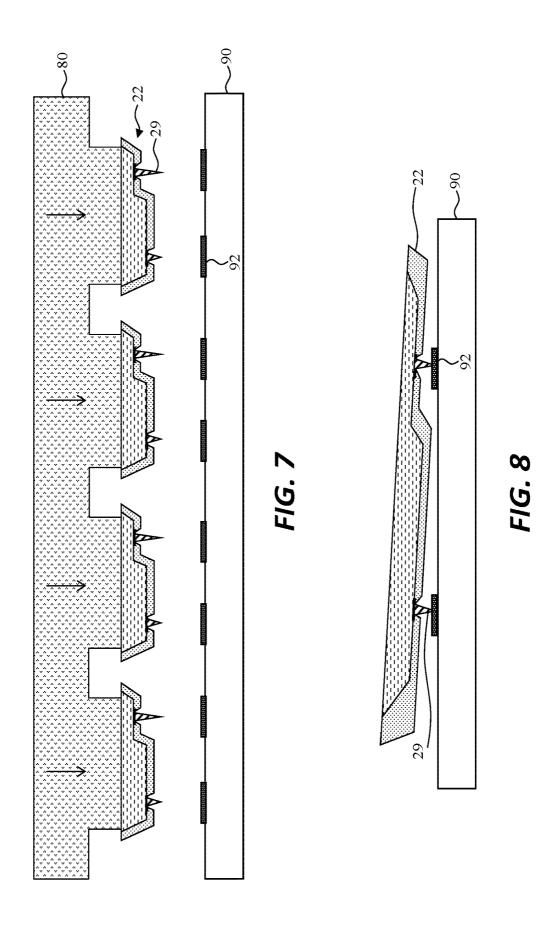

[0075] FIG. 7 is a cross section illustrating micro-transferprinted completed semiconductor devices with a connection post structure and a destination substrate in accordance with an embodiment of the present invention;

[0076] FIG. 8 is a cross section illustrating a completed semiconductor device with a connection post structure and a destination substrate, according to illustrative embodiments of the present invention;

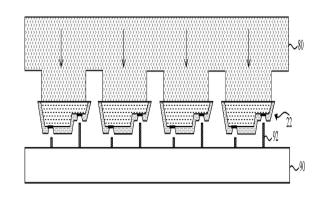

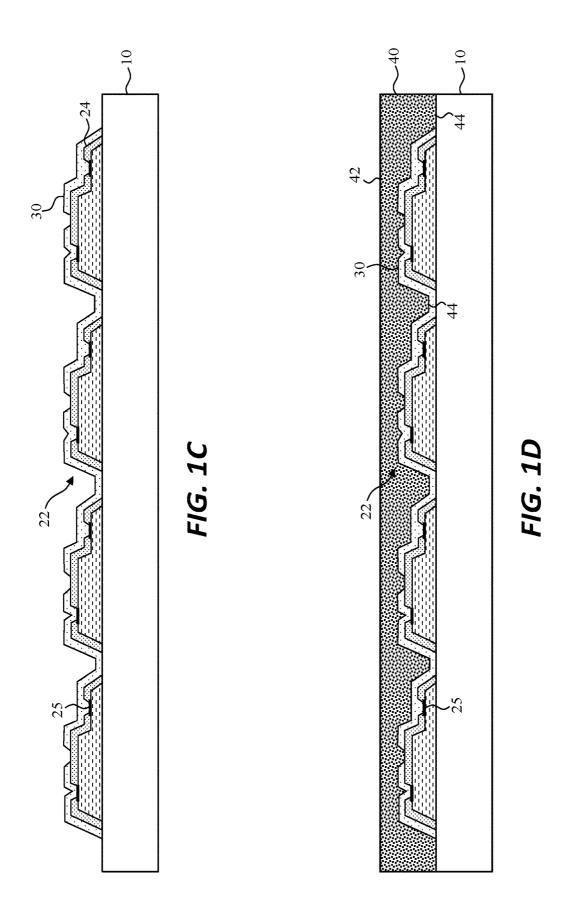

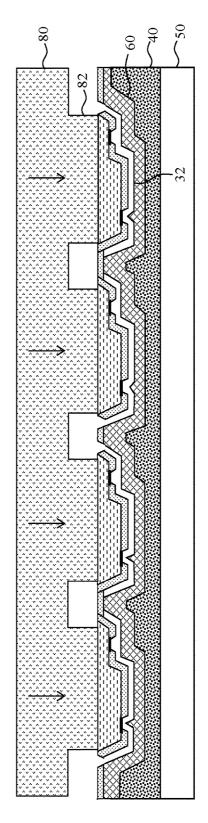

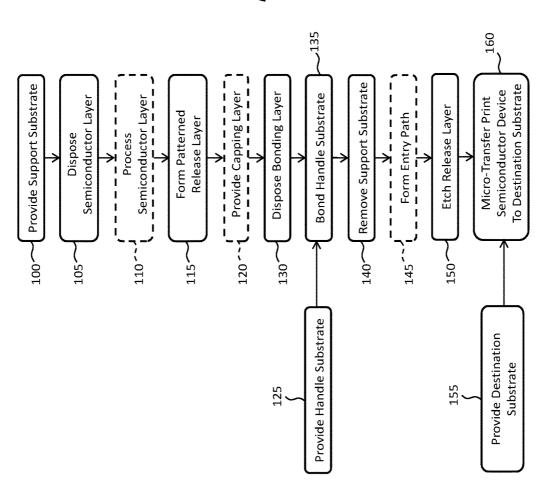

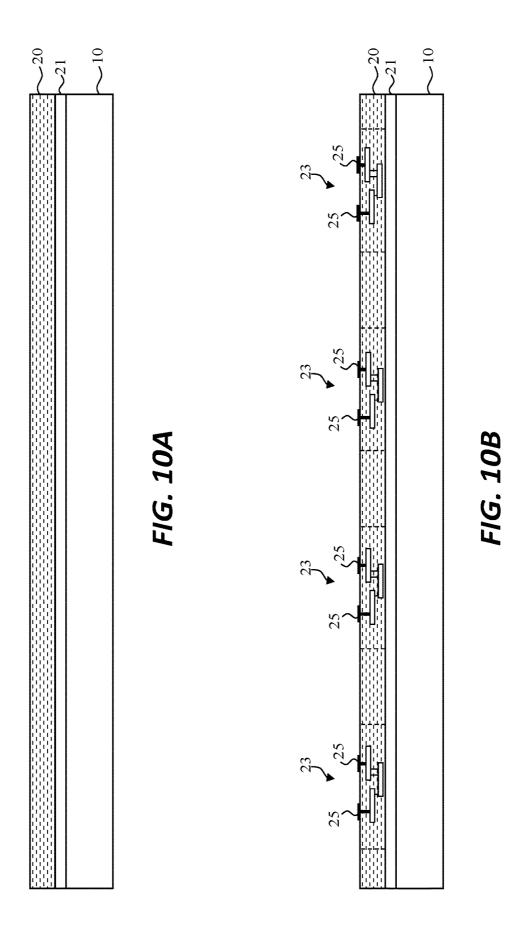

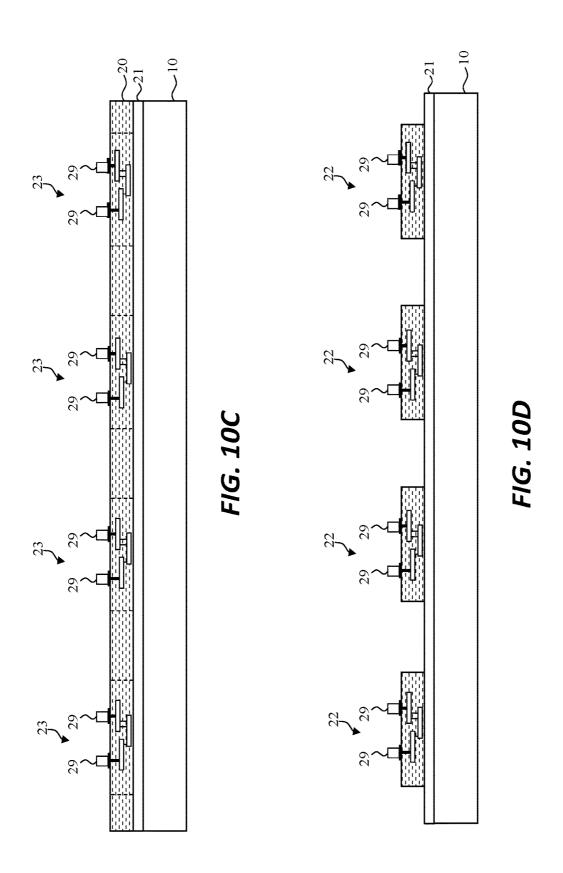

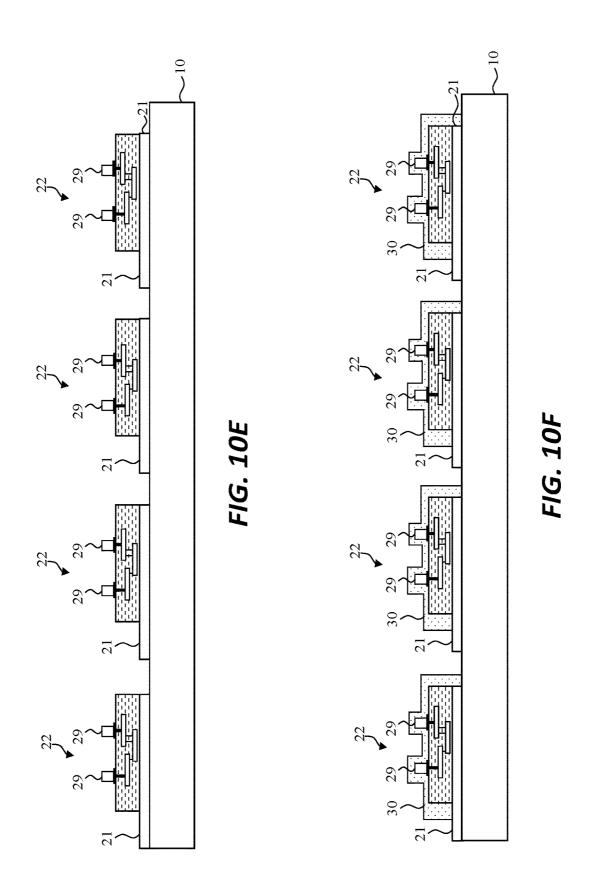

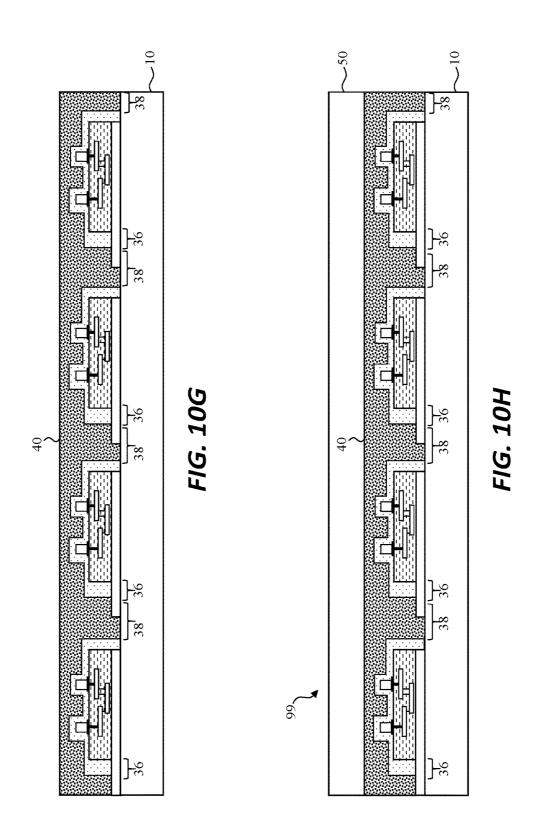

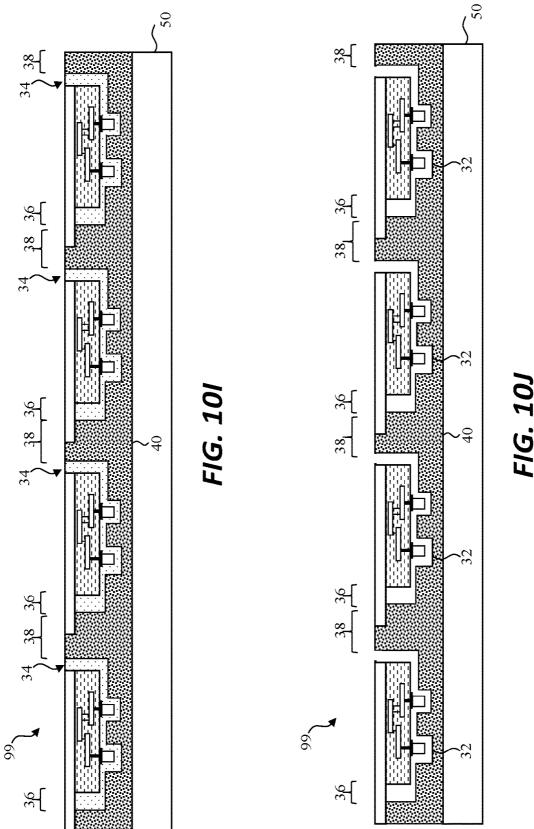

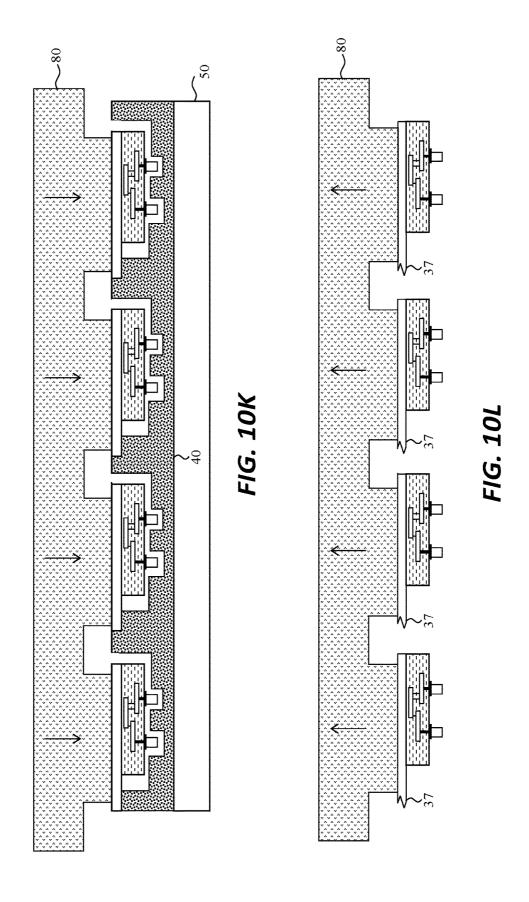

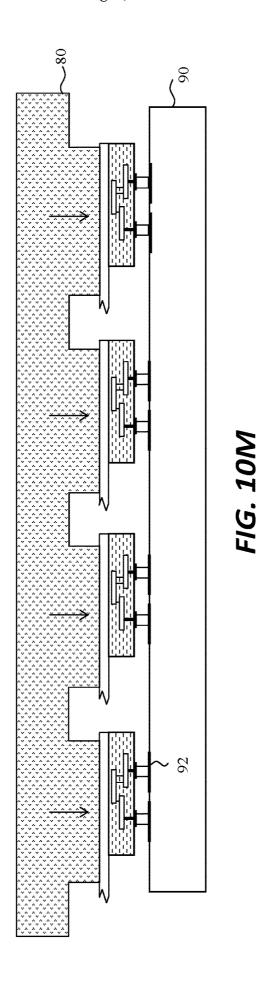

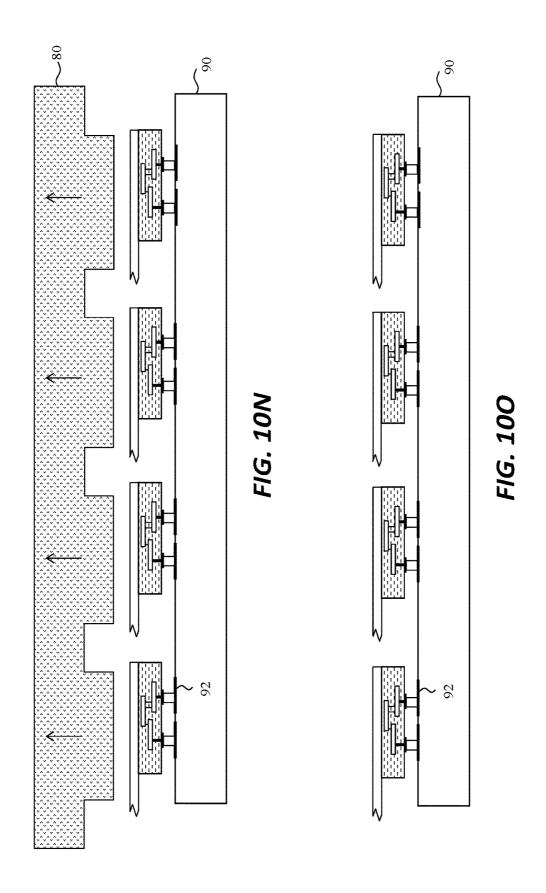

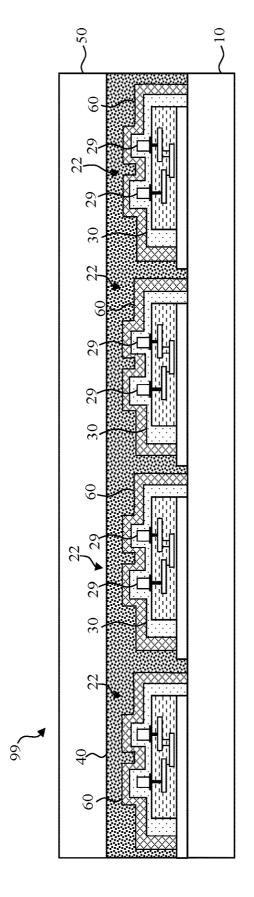

[0077] FIG. 9 is a flow chart illustrating exemplary methods, according to illustrative embodiments of the present invention; FIGS. 10A-10O are successive cross sections illustrating sequential steps in an exemplary method according to illustrative embodiments of the present invention;

[0078] FIG. 11 is a cross section illustrating a completed semiconductor device according to illustrative embodiments of the present invention; and

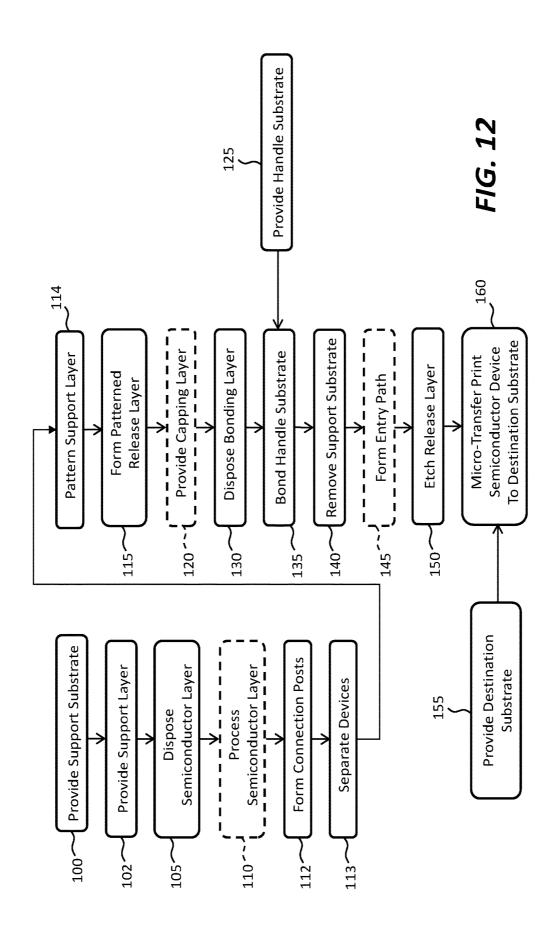

[0079] FIG. 12 is a flow chart illustrating exemplary methods, according to illustrative embodiments of the present invention.

[0080] The features and advantages of the present disclosure will become more apparent from the detailed description set forth below when taken in conjunction with the drawings, in which like reference characters identify corresponding elements throughout. In the drawings, like reference numbers generally indicate identical, functionally similar, and/or structurally similar elements. The figures are not drawn to scale since the variation in size of various elements in the Figures is too great to permit depiction to scale.

## DETAILED DESCRIPTION OF THE INVENTION

[0081] The present invention provides, inter alia, structures and methods to enable micro-transfer printing from devices formed on a sapphire substrate. The present invention also provides, inter alia, structures and methods to enable micro-transfer printing of flipped integrated circuits adhered to a handle substrate. By forming completed semiconductor devices before the removal of a support or growth substrate, photolithographic processing steps that would otherwise disable or destroy release layers and structures needed for transfer printing (e.g., micro-transfer printing) are performed before the construction of the release layer. Thus, once a support or growth substrate is removed, a release layer can be etched and completed semiconductor devices can be transfer printed (e.g., micro-transfer printed) without exposing the completed semiconductor device or release layer to destructive photolithographic process steps. Completed semiconductor devices are otherwise functional devices that do not necessarily include the electrical conductors necessary for providing electrical power to the completed semiconductor devices.

[0082] According to some embodiment of the present invention, and referring to FIGS. 1A-1J and FIG. 9, an exemplary method of making a semiconductor structure 99 (FIGS. 1E-1G) suitable for micro-transfer printing includes providing a support substrate 10 in step 100 and forming a completed semiconductor device 22 (i.e., in this exemplary method by disposing one or more semiconductor layers 20 in, on, or over the support substrate 10) in step 105 (as shown in FIG. 1A). A completed semiconductor device 22

can be formed by disposing one or more layers or substructures on a support substrate 10. The one or more semiconductor layers 20 can optionally be processed in step 110 to make completed semiconductor devices 22 (as shown in FIG. 1B). The processing can include, for example, patterning materials, adding other materials, and forming structures.

[0083] In some embodiments, a support substrate 10 comprises at least one of glass, plastic, semiconductor, compound semiconductor, sapphire (e.g., aluminum oxide or  $\mathrm{Al_2O_3}$ ), ceramic, quartz, silicon, GaAs, GaN, InP, SiC, GaP, GaSb, AlN, an MgO. A support substrate 10 can be a different other substrate suitable for photolithographic processing. A support substrate 10 can be substantially transparent, for example 50%, 70%, or 90% transparent to at least one of visible, UV, and IR electromagnetic radiation. A support substrate 10 can include multiple layers, can include one or more semiconductor layers 20, can be a growth substrate, or can include a growth or semiconductor seed layer on which the one or more semiconductor layers 20 are formed or disposed. A support substrate 10 can be crystalline or have a crystalline layer.

[0084] One or more semiconductor layers 20 can be organic or inorganic, can be crystalline, can be a semiconductor, can be a compound semiconductor, can be doped (e.g., implanted), for example with p or n doping to provide desired electrical structures and functions, or any combination thereof. A semiconductor layer in the one or more semiconductor layer 20 in a completed semiconductor device 22 can include one or more of GaN, Si, InP, SiGe, and GaAs. Each of the one or more semiconductor layers 20 can be formed or disposed in step 105 using photolithographic processes including, for example, evaporation or sputtering. In some embodiments, at least one of the one or more semiconductor layers 20 is formed or disposed using a chemical vapor deposition, molecular/atomic layer deposition, physical vapor deposition, pulsed laser deposition or epitaxy method. In some embodiments, a support substrate 10 is a semiconductor substrate and disposing one or more semiconductor layers 20 in, on, or over the support substrate 10 (step 105) includes doping (e.g., implanting) a portion or layer of a semiconductor substrate (e.g., support substrate 10) to form the one or more semiconductor layers 20. In some embodiments, disposing one or more semiconductor layers 20 in, on, or over a support substrate 10 (step 105) includes growing the one or more semiconductor layers 20 on the support substrate 10 or on a growth layer on the support substrate 10, for example using epitaxial techniques. In these embodiments, the support substrate 10 can be, but is not necessarily, a crystalline semiconductor substrate or sapphire substrate. In some embodiments, a support substrate 10 is a sapphire substrate. In some embodiments, a support substrate 10 is a crystalline semiconductor substrate. [0085] The one or more semiconductor layers 20 can be optionally processed in step 110 using photolithographic methods, including, for example, evaporation, sputtering, CVD, annealing, or masking using photoresist, exposure to patterned radiation, and etching. One or more semiconductor layers 20 can be patterned and structured and additional layers and structures can be formed on or in the one or more semiconductor layers 20, for example, patterned dielectric layers 24 or patterned conductors such as electrical contacts 25 formed, as shown in FIG. 1B. Electrical contacts 25 can be a metalized portion of one or more of the semiconductor

layers 20 or a patterned metal layer over one or more of the semiconductor layers 20 (e.g., with Ag, Al, Ni, Ti, Au, Pd, W, or metal alloys) or simply a designated portion of one or more of the semiconductor layers 20 (e.g., designated for forming electrical connections) and are, in any case, portions of the completed semiconductor device 22 to which electrical connections can be made and power and signals provided to operate the completed semiconductor device 22. In some embodiments, a completed semiconductor device 22 is formed of one or more semiconductor layers 20 and any additional layers and structures necessary to function as intended. In some embodiments, a completed semiconductor device 22 comprises a dielectric layer 24 (e.g., a patterned dielectric layer). A plurality of completed semiconductor devices 22 can be disposed on the support substrate 10 (as shown in FIG. 1B, for example).

[0086] In some embodiments, a completed semiconductor device 22 includes all of the elements necessary to function but does not necessarily include electrical connections to external power or signal sources that enable device operation, or necessarily include protective layers. FIG. 1B illustrates a horizontal LED structure with shaped, structured, and doped (e.g., implanted) semiconductor layers 20, a patterned dielectric layer 24 that defines vias, and two electrical contacts 25 through which electrical power can be transmitted to the semiconductor layers 20 to cause the completed semiconductor device 22 to operate. In FIG. 1B, the completed semiconductor device 22 results all of the photolithographic steps, such as processing and patterning steps, to make the completed semiconductor device 22 functional. A functional completed semiconductor device 22 is a device that provides a desired electronic, optical, thermal, mechanical, magnetic, electric field, photonic, or optoelectronic effect when provided with power but does not include the interconnections necessary to provide power or control signals, such as electrical power or control signals (e.g., from a controller).

[0087] Referring next to FIG. 1C, a patterned release layer 30 is formed or disposed on or over the completed semiconductor device 22 and optionally at least partly in contact with the support substrate 10 (as shown) in step 115. In some embodiments, a patterned release layer 30 does not contact a support substrate 10. A patterned release layer 30 can be formed or disposed using photolithographic methods and materials and can include germanium, Si, TiW, Al, Ti, a lift-off resist, or other polymers. In some embodiments, a patterned release layer 30 material can etch in developer, is not photo-active, or can etch at a higher temperature than photo-active materials such as photo-resists (e.g., greater than 200° C., 300° C., or 400° C.). In some embodiments, a patterned release layer 30 forms a gap 32 or space, for example, after etching the patterned release layer 30 material. For example, a gap can be formed between a completed semiconductor device 22 and a bonding layer 40 after the patterned release layer 30 has been removed.

[0088] Referring to FIGS. 1D and 1E, a handle substrate 50 is provided in step 125, for example, a glass substrate or a plastic substrate. A conformable and curable bonding layer 40 is disposed on the patterned release layer 30 (as shown in FIG. 1D) or on the handle substrate 50 (or on an optional capping layer, discussed further subsequently with respect to FIG. 2C) in step 130. When a conformable and curable bonding layer 40 is disposed on a patterned release layer 30, a portion may also be disposed on a support substrate 10 (as

shown in FIG. 1D). A conformable and curable bonding layer 40 can have a substantially planar side 42 opposite a non-planar side 44 closer to a completed semiconductor device 22. A handle substrate 50 can be substantially transparent, for example 50%, 70%, or 90% transparent to at least one of visible, UV, and IR electromagnetic radiation. A bonding layer 40 can be, for example, a curable resin, epoxy, SU-8, a metal layer, a metal alloy layer, a solder layer, or AuSn. The handle substrate 50 is located in contact with the bonding layer 40 and bonded to the completed semiconductor devices 22, for example, by curing the bonding layer 40 in step 135 (as shown in FIG. 1E) by providing heat, by cooling, or by providing electromagnetic radiation (e.g., UV light) to the bonding layer 40, for example through the handle substrate 50. Curing a bonding layer 40 can include forming a chemical reaction in a material of the bonding layer 40 or hardening the bonding layer 40, or by facilitating a phase change from a liquid to a solid (as with a solder). A bonding layer 40 can be cured by exposing the bonding layer 40 material to light or heat (for example if the bonding layer 40 is a UV-curable resin) or by exposing the bonding layer 40 to heat to melt a metal or metal alloy, disposing a structure in contact with the melted metal or metal alloy, and then cooling the metal. Thus, in some embodiments of the present invention, a metal or metal alloy bonding layer 40 is deposited, heated to melt the metal bonding layer 40 to a liquid, a handle substrate 50, a capping layer 60, or a release layer 30 is brought into contact with the melted liquid metal bonding layer 40, and the melted metal bonding layer 40 is cooled to a solid to adhere the bonding layer 40 to the handle substrate 50, capping layer 60, or release layer 30.

[0089] Referring to FIG. 1F, the support substrate 10 is removed to expose the completed semiconductor device 22 and optionally expose a portion of the patterned release layer 30 to the local environment (as shown) in step 140. In some embodiments, removing a support substrate 10 to expose a completed semiconductor device 22 comprises removing one or more additional layers (e.g., dielectric layers, spacing layers, adhesion layers, growth layers, or removal layers) disposed between the support substrate 10 and the completed semiconductor device 22. If at least a portion of the patterned release layer 30 is not exposed, an entry path 34 is formed to expose a portion of the patterned release layer 30 (as shown in FIG. 2H, and discussed further subsequently) in step 145. For example a portion of a layer that partially covers a patterned release layer 30 can be removed to form an entry path 34. A support substrate 10 can be removed, for example, by one or more of laser liftoff, ablation, laser ablation, etching, and grinding. In some embodiments, both grinding and another removal technique, such as etching, are used.

[0090] As shown in FIG. 1G, the release layer 30 is removed in step 150, for example by etching with  $\mathrm{H_2O_2}$ ,  $\mathrm{XeF_2}$ ,  $\mathrm{HCl}$ ,  $\mathrm{HF}$ , trimethylammonium hydroxide (TMAH), or oxygen plasma. The selection of etchant can depend on the material of the patterned release layer 30. For example,  $\mathrm{H_2O_2}$  or  $\mathrm{XeF_2}$  can be used with a Ge, W, or TiW release layer 30,  $\mathrm{XeF_2}$  can be used with a Si release layer 30, HCl acid mixtures can be used with an Al or Ti release layer 30, TMAH-based developers can be used with a lift-off resist release layer 30, and oxygen plasma can be used with polyimide, epoxy, PMMA, or other organic release layers 30. In some embodiments, an etchant is benign to materials found in or exposed on the surface of a completed semi-

conductor device 22, a bonding layer 40, or both. After etching, a patterned release layer 30 forms a gap 32 or space between a completed semiconductor devices 22 and a bonding layer 40. Referring to FIG. 1G, the release layer 30 is patterned so that a tether 36 physically connects the completed semiconductor devices 22 to an anchor 38 portion of the bonding layer 40 and holds the completed semiconductor devices 22 in place. Generally, an anchor 38 can be a portion of a handle substrate 50 or a layer disposed on the handle substrate (e.g., between the handle substrate 50 and a completed semiconductor device 22), such as, for example, a bonding layer, a capping layer (not shown in FIG. 1G), or a dielectric layer 24. In the illustrative embodiment illustrated in FIG. 1G, the tether 36 is an interface to a post forming the anchor 38. In this embodiment, the anchor 38 is a portion of the bonding layer 40. The interface can, for example, provide a weak adhesion, for example adhesion provided by van der Waal's forces, and can be an interface with or of metal such as gold, tin, or a solder disposed on a portion of the completed semiconductor device 22.

[0091] Once the release layer 30 is etched, the completed semiconductor devices 22 can be micro-transfer printed in step 160, as illustrated in FIG. 1H (shown with an inverted orientation from FIG. 1G), with a stamp 80 (e.g., an elastomeric stamp, for example comprising PDMS) comprising stamp pillars 82 that press against and adhere to the completed semiconductor devices 22 and is then separated from the handle substrate 50 (as shown in FIG. 11). Referring to FIG. 1J, the completed semiconductor devices 22 are brought into aligned contact with a destination substrate 90 (the destination substrate 90 is provided in step 155) and adhered to the destination substrate 90. In some embodiments, electrical contacts 25 of a completed semiconductor device 22 are electrically connected to contact pads 92 formed or disposed on a destination substrate 90. Contact pads 92 can be electrically connected to an electrical circuit, for example through electrical conductors on the destination substrate 90 (not shown), to provide electrical power and signals to a completed semiconductor device 22.

[0092] In some embodiments of the present invention, and referring to FIGS. 2A-2K, an alternative exemplary method of making a semiconductor structure 99 (as shown in FIG. 2G-2I) suitable for micro-transfer printing includes additional steps and elements as compared to the process and semiconductor structure 99 described with respect to FIGS. 1A-1J. Referring to FIG. 2A and again to FIG. 9, a support substrate 10 is provided in step 100 that includes a removal layer 26. A removal layer 26 can be an ablation layer or an etch-stop layer and can be a layer of a support substrate 10 or a layer disposed on the support substrate 10. A removal layer 26 can be patterned. Ablation and etch-stop layers can include one or more of (i) SiO<sub>x</sub> or SiN<sub>x</sub> deposited by, for example, plasma-enhanced chemical vapor deposition (PECVD) and (ii) organic layers with or without particles. Additional layers, such as buffer layers (e.g., C-GaN, AlGaN, or doped GaN) or one or more semiconductor growth layers can be provided as well.

[0093] A completed semiconductor device 22 (i.e., in this exemplary method by disposing one or more semiconductor layers 20 in, on, or over the support substrate 10) in step 105 (as shown in FIG. 2A). A completed semiconductor device 22 can be formed by disposing one or more layers or substructures on a support substrate 10. The one or more semiconductor layers 20 can be processed in step 110 to

form the completed semiconductor device 22 (as shown in FIG. 2B) over or in contact with the removal layer 26, as described previously. In some embodiments, and as is shown in FIG. 2B, a dielectric layer 24 of a completed semiconductor device 22 is patterned to extend beyond the completed semiconductor device 22 (e.g., for use in forming anchors 38 and/or tethers 36).

[0094] Referring next to FIG. 2C, a patterned release layer 30 is formed or disposed on or over the completed semiconductor device 22 in step 115. As shown in FIG. 2C, a patterned release layer 30 can be at least partially in contact with a dielectric layer 24 rather than a support substrate 10 (in contrast to what is shown in FIG. 1C). In some embodiments (not shown), a patterned release layer 30 is at least partially in contact with a removal layer 26. Referring to FIG. 2C, a capping layer 60 is disposed on the release layer 30 in step 120. A capping layer 60 is optional and is not present in some embodiments. A capping layer 60 can be deposited using photolithographic methods such as evaporation, sputtering, plating, atomic layer deposition (ALD), or coating and can include organic or inorganic materials such as SiN<sub>x</sub>, SiO<sub>x</sub>, copper, nickel, or other materials. A capping layer 60 can be non-planar, patterned, structured or shaped, can stiffen the semiconductor structure 99, or can include multiple layers of different materials that can be selected and formed to control acoustic or mechanical vibrations. Referring to FIGS. 2D and 2E, a handle substrate 50 is provided in step 125 and a conformable and curable bonding layer 40 is disposed on the optional capping layer 60 (as shown) or on the handle substrate 50 (not shown), in step 130. A conformable and curable bonding layer 40 can have a substantially planar side 42 opposite a non-planar side 44 closer to a completed semiconductor device 22. A handle substrate 50 can be substantially transparent, for example 50%, 70%, or 90% transparent to at least one of visible, UV, and IR electromagnetic radiation. A bonding layer 40 can be, for example, a curable resin, epoxy, SU-8, a metal layer, a metal alloy layer, a solder layer, or AuSn.

[0095] The handle substrate 50 is located in contact with the bonding layer 40 and bonded to the completed semiconductor devices 22 by, for example, curing the curable bonding layer 40 in step 135 (as shown in FIG. 2E), for example by providing time, heat, cooling, or electromagnetic radiation to the bonding layer 40, for example through the handle substrate 50. The material of the capping layer 60 provided in step 120 can be selected to prevent unwanted interactions between the release layer 30 etching chemistry and the bonding layer 40. For example, in some embodiments, an etchant that is suitable for etching the release layer 30 might also undesirably etch the bonding layer 40, resulting in compromise a micro-transfer printing process for the completed semiconductor device 22 if not for the presence of the optional capping layer 60.

[0096] Referring to FIG. 2F, the support substrate 10 is removed in step 140. In some embodiments, and as shown in FIG. 2F, a removal layer 26 is exposed to electromagnetic radiation 70 (for example from a laser) through a support substrate 10 (i.e., wherein the support substrate 10 is at least partially transparent to the electromagnetic radiation 70) to decompose at least a portion of the removal layer 26, as illustrated with shading in the removal layer 26 in FIG. 2F. In some embodiments, a removal layer 26, for example an ablation layer, absorbs is heated by the electromagnetic radiation 70 and evaporates or sublimates to a gas or plasma

Aug. 9, 2018

10

that forcefully dissociates a support substrate 10 from the removal layer 26. Ablation layers can be selected to complement the support substrate 10 or layer materials formed on or in the support substrate 10. An ablation layer can be the same material as is found in the semiconductor layers 20, for example GaN. Moreover, in some embodiments, GaN can serve as an ablation layer for sapphire or AlN support substrates 10. GaNAs or InGaNAsSb can be included in ablation layers or materials grown on GaAs substrates. InGaAs, InGaAsP, AlInGaAs, or AlInGaAsP can be included in ablation layers or materials grown on InP substrates. In some embodiments, black chromium can be an ablation layer. Ablation layers can include organic materials such as vaporizable polymer or materials that incorporate light-absorbing particles such as carbon black or oxidized chromium and that can absorb electromagnetic radiation, facilitate ablation layer heating, and ablate of the layer.

[0097] Typically, laser ablation transfers momentum to a surface and, in some embodiments of the present invention, can form a shock wave (an acoustic or mechanical pulse of high pressure) that passes into and through a completed semiconductor device 22 (or completed semiconductor devices 22, if multiple are present) and can damage the completed semiconductor device 22. A capping layer 60 (and, in some embodiments, to some extent, a bonding layer 40 and/or a release layer 30) can dissipate, disperse, deflect, reflect, or absorb the shock wave and prevent or mitigate damage to a completed semiconductor device 22. The layers, materials, and structure of a capping layer 60 can be specifically designed to prevent or mitigate damage to a completed semiconductor device 22. In some embodiments, a release layer 30 comprises germanium, which has a large acoustic impedance and can therefore effectively reflect or redirect at least a portion of a shock wave. In some embodiments of the present invention, laser ablation can be used to remove a support substrate 10 from a semiconductor structure 99 used in a flip-chip micro-transfer printing process, as shown in FIG. 2G.

[0098] In some methods and micro-transfer printable semiconductor structure 99 designs, removal of a support substrate 10 exposes the release layer 30 (e.g., as shown in FIG. 1F). However, in some embodiments, and as illustrated in FIG. 2G, a release layer 30 is not exposed in step 140. For example, a release layer can be covered by a dielectric layer 24. In some embodiments, a dielectric layer 24 is patterned to expose a portion of a release layer 30, as shown in FIG. 1F. However, in the illustrative embodiment shown in FIGS. 2F and 2G, the patterned dielectric layer 24 is not exposed when the support substrate 10 is removed. Thus, as illustrated in FIG. 2H, in step 145 an entry path 34 is formed to expose a portion of the patterned release layer 30. An entry path 34 can be formed, for example, by pattern-wise etching a dielectric layer 24 (or other layer disposed over a patterned release layer 30). In some embodiments, the step of forming an entry path 34 is the same step as removing a support substrate 10. That is, in some embodiments, removing a support substrate 10 forms an entry path 34 by exposing a portion of a release layer 30. As used herein, an "exposed" layer or element is one that is exposed to the local environment, can be exposed to a processing material such as a chemical etchant, can have materials deposited thereon, or any combination thereof. In some embodiments, a layer (e.g., a support substrate 10) is removed to expose an element (e.g., a completed semiconductor device 22) while one or more other layers (e.g., dielectric layers or a remaining portion of a removal layer 26) remain that need to be removed to provide an exposed element. For example, in some embodiments, a support substrate 10 is removed to expose a completed semiconductor device 22 and subsequently a sacrificial dielectric layer and/or remaining portion of a removal layer 26 disposed on the completed semiconductor device 22 is removed thereby providing an exposed completed semiconductor device 22.

[0099] Referring to FIG. 2I, the release layer 30 is removed in step 150, for example by etching as described above with respect to FIG. 1G. After etching, the release layer 30 forms a gap 32 or space between the completed semiconductor devices 22 and the capping layer 60. A release layer 30 and entry paths 34 are patterned so that one or more tethers 36 physically connect a completed semiconductor devices 22 to an anchor 38 disposed on the handle substrate 50 (e.g., wherein the anchor 38 is a portion of a dielectric layer 24, a capping layer 60, a handle substrate 50, or another layer disposed on the handle substrate 50) holds the completed semiconductor device 22 in place. Referring to FIG. 2I, the completed semiconductor devices 22 are physically connected to the anchors 38, where are portions of the dielectric layer 24. In some embodiments, a plurality of tethers 36 physically connect each completed semiconductor device 22 to one or more anchors 38 (e.g., a plurality of anchors 38). In some embodiments, a plurality of anchors 38 formed from portions of a bonding layer are physically connected to each completed semiconductor device 22. In the illustrative embodiment illustrated in FIG. 2I, each tether 36 is a portion of the dielectric layer 24. A tether 36 can be disposed in a common plane with an entry path 34 or an entry path 34 can extend through or around a tether 36. A tether 36 can be separated or broken (e.g., fractured) if pressure is applied to a completed semiconductor device 22. In some embodiments, a tether 36 is separated during transfer printing (e.g., by overcoming van der Waals forces that adhere a completed semiconductor device 22 to an anchor 38). In some embodiments, a tether 36 is fractured during transfer printing (e.g., wherein pressure fractures the dielectric material that the tether 36 is made from).

[0100] Once the release layer 30 is etched, the completed semiconductor devices 22 can be micro-transfer printed in step 160, as illustrated in FIG. 2J (shown with an inverted orientation from FIG. 2I), with a stamp 80 (e.g., an elastomeric stamp, for example comprising PDMS) comprising stamp pillars 82 that press against and adhere to the completed semiconductor devices 22 and is then separated from the handle substrate 50 (as shown in FIG. 2K). The completed semiconductor devices 22 are brought into aligned contact with a destination substrate 90 and micro-transfer printed to the destination substrate 90, as shown and described with respect to FIG. 1J.

[0101] Referring next to FIG. 3A, in some embodiments, semiconductor layer(s) 20 are formed in a support substrate 10, for example by doping (e.g., implanting) the support substrate 10 to form a layer on or at a surface (e.g., within the surface) of the support substrate 10 in step 105 that is the semiconductor layer(s) 20. The semiconductor layer(s) 20 can be processed in step 110 to form the completed semiconductor devices 22 (as shown in FIG. 3B). Thus, forming semiconductor layer(s) 20 in step 105 can include forming

a layer on the support substrate 10 (as shown in FIGS. 1A, 2A) or forming a layer in the support substrate 10 (as shown in FIG. 3B).

[0102] In some embodiments, and as shown in FIG. 4, a removal layer 26 is a portion of a completed semiconductor devices 22 and possibly other layers or a portion of a support substrate 10 (in which case the removal layer 26 includes a portion or layer of the support substrate 10). For example, in some embodiments, ablation can remove the portion of the structure indicated with the heavy dashed rectangle. Thus, in some embodiments, removing a support substrate 10 (e.g., as in step 140) comprises exposing semiconductor layer(s) 20 or completed semiconductor device 22 to electromagnetic radiation 70 through the support substrate 10 to decompose a portion of the semiconductor layer(s) 20 or the completed semiconductor device 22 and form a shock wave in a semiconductor structure 99. A capping layer 60, if present, can disperse, reflect, deflect, or absorb the shock wave.

[0103] Referring to FIG. 2K, each completed semiconductor device 22 has at least one individual broken (e.g., fractured) tether 36 as a consequence of micro-transfer printing. A broken tether 36 can be a fractured structure, as in FIG. 2K. A separated tether 36 can be an interface formed between two elements for which one element is removed, as in FIG. 1I. However, before tethers 36 are broken (as shown in FIG. 2J), two or more tethers 36 can be part of a common structure and be physically connected to a common anchor 38. Anchors 38 can be any portion of a semiconductor structure 99 that is not the completed semiconductor device 22, for example a bonding layer 40 (as shown in FIG. 1G), a dielectric layer 24 (as shown in FIG. 21), or a capping layer 60

[0104] Referring to the plan view of FIG. 5 and corresponding to the cross section of FIG. 1G viewed through the handle substrate 50 and excluding non-anchor portions of the bonding layer 40, in some embodiments, at least two of the plurality of completed semiconductor devices 22 are tethered to anchors 38 that are portions of an anchor structure 39 that is a ridge of material (e.g., that physically connects to each of two or more completed semiconductor devices 22 at an interface that is a tether 36). In the illustrative embodiment of FIG. 5, each anchor structure 39 comprises three anchors 38 physically connected to the tethers 36 of three corresponding completed semiconductor devices 22. In some embodiments, an anchor structure 39 comprises a plurality of anchors 38 (e.g., two or more or three or more anchors).

[0105] In some embodiments of the present invention (not shown), a completed semiconductor device 22 has a semiconductor structure with a planar surface adjacent to a patterned release layer 30 opposite a support substrate 10 so that electrical contacts 25 of the completed semiconductor device are in a common plane. This arrangement facilitates electrical connection between the electrical contacts 25 and contact pads 92 on a destination substrate 90. In some embodiments, contact pads 92 are likewise in a common plane on a surface of a destination substrate 90, so that electrical contacts 25 in a common plane can both contact each contact pad 92 at the same time. However, in some embodiments and as illustrated in FIGS. 1B-C and 2C, a completed semiconductor device 22 has a semiconductor structure with a non-planar surface adjacent to a patterned release layer 30 and opposite a support substrate 10 so that electrical contacts 25 are not in a common plane. Thus, it can be necessary to adjust the structure or arrangement of the completed semiconductor device 22 or destination substrate 90 in order to form an electrical connection between the completed semiconductor device 22 and contact pads 92 on the destination substrate 90 when the completed semiconductor device 22 is transfer printed (e.g., micro-transfer printed) to the destination substrate 90.

[0106] In some embodiments, and as shown in FIG. 1J, a destination substrate 90 has a non-planar surface with a topography that corresponds to a non-planar completed semiconductor device 22 surface. Accordingly, contact pads 92 (which provide at least a portion of the surface topography of a destination substrate 90) can have different heights that correspond to different locations of a non-planar completed semiconductor device 22 surface, in particular the different heights of the electrical contacts 25 of the completed semiconductor structures 22 over the destination substrate 90, so that the contact pads 92 can readily make electrical connections with the electrical contacts 25.